Wie nutzt man programmierbare Logik bei der Entwicklung von Applikations-Software?

Der Einsatz von FPGAs und programmierbarer SoCs bietet großes Potential, um die Leistung darauf basierender Anwendungs-Software signifikant zu beschleunigen. Es kommt nur auf den Einsatz der richtigen Toolchains und Bibliotheken an.

Anbieter zum Thema

FPGAs und heterogene SoCs (system on chip) ermöglichen Applikationsentwicklern durch ihre Kombination von High-Performance Prozessorkernen mit programmierbarer Logik signifikante Beschleunigungseffekte. Die effiziente Entwicklung derartiger Bausteine erfordert allerdings einen Entwicklungsfluss, der sowohl Industrie-Standard High-Level Bibliotheken, und auch die Frameworks für Computer Vision und Machine Learning unterstützt, einschließlich OpenCV, OpenVX, FFmpeg und Caffe.

Die Kombination dieser High-Level Frameworks und der Beschleunigungsfähigkeit erzielt bei der Applikationsentwicklung einen signifikanten Zuwachs an Performance in Edge- und Cloud-basierten Applikationen. Das gilt für die Vision-gestützte Robotik ebenso wie für die Genom-Verarbeitung. In einigen Fällen realisiert diese Beschleunigung eine Rekord-Performance - wie es in der Genom-Verarbeitung am Children’s Hospital of Philadelphia (CHOP) und im Edico Genome Projekt der Fall war. CHOP und Edico Genome haben einen neuen Weltrekord bei der schnellen Umsetzung kompletter menschlicher Genome in Datensätze aufgestellt, die für die weitere Forschung verwertbar sind. Dabei wurden 1000 pädiatrische Genome mit der DRAGEN Genome Pipeline von Edico Genome in nur zwei Stunden und 25 Minuten bearbeitet. Diese Leistung wurde möglich durch die Cloud-basierte Beschleunigung mit High-Performance All Programmable FPGAs, wie sie über die Amazon Web Service EC2 F1 Instance erhältlich sind.

Die grundlegende Technologie, die es Applikationsentwicklern ermöglicht, das Potenzial der programmierbaren Logik gewinnbringend zu nutzen, ist die High-Level Synthese (HLS). HLS bietet Algorithmen, die in C, C++ oder OpenCL spezifiziert sind, um sie direkt in der programmierbaren Logik zu beschleunigen. Um die Produktivität der Entwicklung zu maximieren, sollte das HLS-Tool dabei ein Teil der Toolkette zur Entwicklung und eines Ökosystems sein, die High-Level Frameworks und Bibliotheken unterstützen.

Toolchains

Applikationsentwicklern, die Cloud-basierte Applikationen mit Xilinx FPGAs oder Edge-basierte heterogene SoC-Applikationen planen, stehen zwei dieser Toolketten zur Verfügung: SDAccel für Cloud-basierte, und SDSoC für Edge-basierte Entwicklungen.

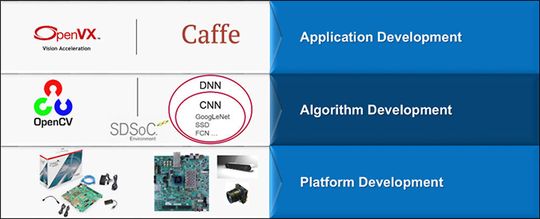

Beide Tool-Chains bieten unterstützende Ökosysteme mit Acceleration Stacks, die zur Beschleunigung von Frameworks und Bibliothek-Funktionen in programmierbarer Logik geeignet sind. Diese Stacks sind: der Reconfigurable Acceleration Stack (RAS) für Cloud-basierte Applikationen, sowie der reVISION Stack für Edge-basierte Applikationen mit Embedded Vision.

Beide Stacks, RAS und reVISION, sind jeweils in drei distinktive Layer unterteilt, ganz ähnlich dem siebenschichtigen OSI-Modell der Telekommunikation, mit dem viele Entwicklern gut vertraut sind. Der niedrigste Layer ist der Plattform-Layer, sowohl im RAS- wie im reVISION-Stack. Dies ist die Hardware-Plattform, die den ausgewählten All Programmable FPGA oder SoC-Baustein enthält, auf dem die übrigen Teile des Stacks implementiert werden.

Allerdings sind die in den beiden Stacks eingesetzten Technologien unterschiedlich. Wenn man mithilfe des reVISION-Stack entwickelt, stammt der Zielbaustein aus der All Programmable Zynq-7000 SoC- oder der Zynq UltraScale+ MPSoC-Familie (Bild 1). Die RAS-Plattform hingegen basiert auf dem Einsatz von UltraScale+ FPGAs (Bild 2). Daraus folgt ein Unterschied in den beiden übrigen Layern der Stack. Auf diesen beiden funktional höheren Ebenen erstellt der Entwickler der Applikationssoftware seine Lösung.

(ID:45009878)

:quality(80)/p7i.vogel.de/wcms/b8/20/b8203d9f2b6f6e61bff6c3fda15042d3/0128235802v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/90/79901d8c1934b11223a53cb900b1aa85/das-20building-2092-20bei-20der-20microsoft-zentrale-20in-20redmond-20--20quelle-20coolcaesar-20via-20wikimedia-20commons-5184x2915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/92/3192d2bddbdb052afd8904128dd7aec1/0123884994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/42/b04293b683f177fa6c781c1e00e1770f/0122968330v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/ea/acea3ca6c15e0bd261c8bde5d3fe7bfb/0127825678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/d9/93d9211463a0af86eff0b83c359cd880/0127528428v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/c1/d9c121f0680f16e547502038f5c26481/0130027942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/3d/753d0fa44b344d363e25c91dc0752635/0129134302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9a/ef9a10566eaa807a8fdad9cbff80246f/0126533084v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/f5/47f5a305c48bfcaf3daae7e6b7478a0f/0131065910v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/a8/a9a87353e49fb7432ce35aef31d06ad6/0130134372v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/b2/1eb228a11ff793648167b84e30da4eb3/0129529708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/0a/df0a16a8a74519cf7e4ae26b468a8326/0129511289v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/23/2323167fce16d7a31011ac17a97933c9/0129855253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/e0/5fe00181ea62f890f53af36d03782612/0129630465v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/92/6f92cb791d67b866650a432e847ad8f2/0129693241v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/0e/f30ed4c0e762a250c39013170f3d154a/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/b2/2eb2a82d215c72f59c1fde532c092e87/0131010297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/a7/44a7069736629cbbfa41b74af865ec67/0130322397v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/8c/718c0df3cae4339bb3ea0b799b53e1cd/0131015301v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/21/b12113e8d5357060593e78ad3e396773/0130960706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/f0/4cf066b46a5fcfc430a2454a5e82e801/0129279386v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/27/b9/27b9cfbb678630047f85e1adc55f7df7/0114455762.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/96/4d9621a180cfee96ba85d2da83163461/0105948132.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/05/3405327567eb345e9c0c326a590cd9ae/0105886699.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/89/22896600c7f19a5813fa824ee8207dd4/0122524970v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/cf/e7cf5a22f39eddc3235f047c566b747e/0122159010v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/c4/43c4067994de48347a260c6191e88528/0103046501v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/a1/74a1fcd5d60af69422390e97fbf77dcd/0109296819.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1c/661cd4860acd6/emlix-logo-300x210mm-150dpi-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/5f/bf/5fbfdf326d5dd/rti-logo-color-200px.jpg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/b2/93b2dee2b42d98849c80562a53d8b31e/0128754755v2.jpeg)