Ein Plädoyer für die Verwendung von VHDL-2008

Viele Entwickler setzen – teils aufgrund veralteter Tools, teils aus reiner Gewohnheit – noch auf den früheren VHDL-2002-Standard. Dabei hält VHDL-2008 zahlreiche Erleichterungen und Verbesserungen bereit.

Anbieter zum Thema

Die Beschreibung mit Hardwarebeschreibungssprachen (HDLs) der dritten Generation, wie beispielsweise System-C oder System-Verilog stößt bei den Designern digitaler Systeme auf zunehmendes Interesse. Das gilt insbesondere für sehr komplexe Systeme mit hohem Verifikationsaufwand.

Dabei darf jedoch nicht verkannt werden, dass die etablierten Hardwarebeschreibungssprachen wie VHDL und Verilog gerade für den Entwurf kleiner und mittelgroßer Systeme auch in Zukunft noch sehr gefragt sein werden. Dies liegt neben dem hohen Verbreitungsgrad dieser Sprachen auch an der Tatsache, dass es dafür sehr gut etablierte Simulations- und Synthesewerkzeuge gibt, deren Lizenzen auch von kleinen und mittelständischen Unternehmen kostengünstig erworben werden können.

Vor diesem Hintergrund mag es ein wenig verwundern, dass sich die durch den Standard VHDL-2008 definierten Spracherweiterungen in der Vergangenheit noch recht wenig durchgesetzt haben. Wesentliches Ziel der schon Anfang 2009 als Standard IEEE1076-2008 definierten Überarbeitung von VHDL war es, die Wortfülle zu reduzieren, die einen VHDL-Code im Vergleich zu einem Verilog-Code kennzeichnet [2].

Außerdem wurden neue Operatoren und Datentypen eingeführt, die den digitalen Schaltungsentwurf vereinfachen. Diese Neuerungen wurden recht schnell in den Simulationswerkzeugen implementiert und werden nun zunehmend auch von den Synthesewerkzeugen unterstützt. Daher erscheint es längst überfällig, die bisherige Zurückhaltung bei der Verwendung der Sprachvereinfachungen aufzugeben und die neuen Möglichkeiten des VHDL-2008 Standards in die firmeninternen Kodierungsrichtlinien zu integrieren.

Die nachfolgende Übersicht stellt nur einige der wichtigsten Neuerungen und Vereinfachungen dem älteren Sprachstandard VHDL-2002 an Hand einfacher Beispiele gegenüber. Ein weitergehender Vergleich findet sich in [1] beziehungsweise. in der Definition des VHDL-2008-Standards [3]. In einem Plädoyer zur Verwendung von VHDL-2008 darf allerdings nicht nur auf die vereinfachte VHDL-Syntax und -Semantik eingegangen werden, sondern es muss vielmehr auch vorgestellt werden, in welchem Umfang diese durch Simulations- und Synthesewerkzeuge unterstützt wird.

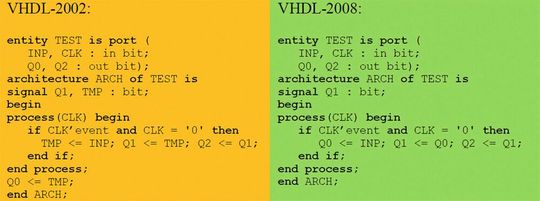

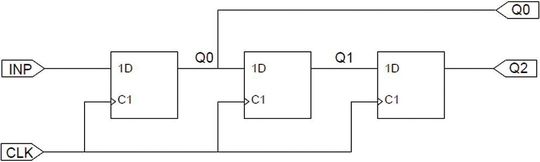

Lesen von Output Ports und neue Vergleichsoperatoren

Im bisherigen VHDL Standard war es verboten, ein als out Port deklariertes Signal auch innerhalb der architecture weiter zu verwenden. Für diesen Zweck war es entweder notwendig, den ungeliebten Port-Modus buffer zu verwenden, oder aber es musste ein lokales Signal deklariert werden.

Dieser zusätzliche Aufwand ist in VHDL-2008 nicht mehr erforderlich. Nun können Signale vom Typ out auch intern weiter verwendet werden. Die nachfolgende Schieberegisterschaltung mit Abzweigung nach dem ersten Flipflop kann in VHDL-2008 ohne Deklaration des lokalen Signals TMP modelliert werden (siehe Listing 1 sowie Bild).

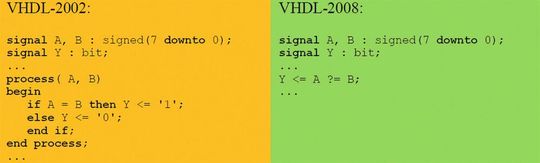

Auch neue Vergleichsoperatoren sind nun in VHDL-2008 vorhanden. Das Ergebnis der Vergleichsoperationen =, /=, <, >, <= oder >= ist vom Typ boolean. Neu ist im Standard VHDL-2008, dass entsprechende synthesefähige Vergleichsoperatoren mit voran gestelltem Fragezeichen definiert sind, deren Ergebnis entweder vom Typ bit oder vom Typ std_logic sein darf. In dem Listing 2 soll das Signal Y gesetzt werden, wenn die Operanden A und B gleich sind.

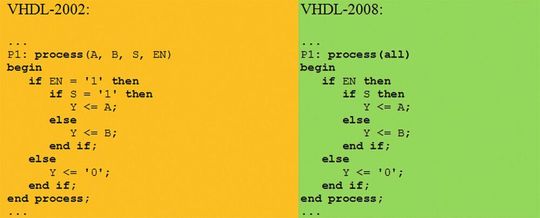

Sensitivityliste kombinatorischer Prozesse

Eine erhebliche Vereinfachung bietet der VHDL-2008 Standard bei der Modellierung kombinatorischer Logik mit Prozessen. Bisher war es für eine korrekte VHDL-Synthese kombinatorischer Logik erforderlich, nicht nur alle Signale, die auf der rechten Seite von Signalzuweisungen stehen, explizit in die Sensitivityliste aufzunehmen, sondern auch alle Signale, die in Bedingungsausdrücken stehen. Diese Anforderung entfällt, wenn das neue VHDL-Schlüsselwort all verwendet wird (Listing 3).

Bedingte und Selektive Signalzuweisungen in Prozessen

In den bisher gültigen VHDL-Standards waren innerhalb von Prozessen nur sequenzielle Anweisungen sowie die unbedingte Signalzuweisung erlaubt. Diese Einschränkung gilt nach dem VHDL-2008 Standard nicht mehr. Nun sind in diesem Standard bedingte und selektive Signalzuweisungen auch innerhalb von Prozessen erlaubt. So ist z.B. eine vereinfachte Modellierung eines Registers mit Enable Eingang möglich.

Datenformat für rationale Festkommazahlen

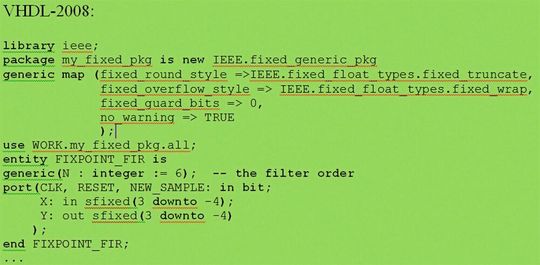

Neuer Bestandteile des VHDL-2008 Standards sind der vorzeichenlose Datentyp ufixed und der vorzeichenbehaftete Datentyp sfixed. Damit werden rationale Zahlen im Q-Format abgebildet. Diese Datentypen repräsentieren Signalvektoren mit positiven und negativen Indices, wobei die positiven Indices dem ggf. vorhandenen Vorzeichen sowie dem ganzzahligem Anteil entsprechen und die negativen Indices dem Bruchteil der Zahl [1]. Die Datentypen sind in der Bibliothek ieee.fixed_pkg mit fester Rundungs-, Überlauf- bzw. Sättigungscharakteristik deklariert.

Alternativ können diese Eigenschaften jedoch auch in einer generischen Bibliotheksvarianten der Standardbibliothek ieee.fixed_generic_pkg definiert werden. Das Listing 4 zeigt die Deklaration einer generischen Festkommabibliothek my_fixed_pkg mit Abschneidecharakteristik (fixed_round_style), Signalüberlauf (fixed_overflow_style) und ohne Schutz bei temporären Überläufen (fixed_guard_bits) [3]. Diese Parameter werden durch eine generic map Anweisung eingestellt.

Listing 4 enthält ebenfalls die Deklaration einer FIR-Filter (Finite-Impules-Response) entity, in der die Eingangs- und Ausgangssignale X bzw. Y im s3Q4-Format verwendet werden.

Die in Bild 2 dargestellte Simulation der Sprungantwort zeigt die in dem Modell verwendete Wertquantisierung der Koeffizienten H, des internen Akkumulators ACCU und des Ausgangssignals Y mit 4 Nachkommastellen entsprechend einer Auflösung von 2-4.

(ID:45610702)

:quality(80)/p7i.vogel.de/wcms/b8/20/b8203d9f2b6f6e61bff6c3fda15042d3/0128235802v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/90/79901d8c1934b11223a53cb900b1aa85/das-20building-2092-20bei-20der-20microsoft-zentrale-20in-20redmond-20--20quelle-20coolcaesar-20via-20wikimedia-20commons-5184x2915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/92/3192d2bddbdb052afd8904128dd7aec1/0123884994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/42/b04293b683f177fa6c781c1e00e1770f/0122968330v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/ea/acea3ca6c15e0bd261c8bde5d3fe7bfb/0127825678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/d9/93d9211463a0af86eff0b83c359cd880/0127528428v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/c1/d9c121f0680f16e547502038f5c26481/0130027942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/3d/753d0fa44b344d363e25c91dc0752635/0129134302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9a/ef9a10566eaa807a8fdad9cbff80246f/0126533084v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/f5/47f5a305c48bfcaf3daae7e6b7478a0f/0131065910v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/a8/a9a87353e49fb7432ce35aef31d06ad6/0130134372v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/b2/1eb228a11ff793648167b84e30da4eb3/0129529708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/0a/df0a16a8a74519cf7e4ae26b468a8326/0129511289v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/23/2323167fce16d7a31011ac17a97933c9/0129855253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/e0/5fe00181ea62f890f53af36d03782612/0129630465v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/92/6f92cb791d67b866650a432e847ad8f2/0129693241v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/0e/f30ed4c0e762a250c39013170f3d154a/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/b2/2eb2a82d215c72f59c1fde532c092e87/0131010297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/a7/44a7069736629cbbfa41b74af865ec67/0130322397v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/8c/718c0df3cae4339bb3ea0b799b53e1cd/0131015301v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/21/b12113e8d5357060593e78ad3e396773/0130960706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/f0/4cf066b46a5fcfc430a2454a5e82e801/0129279386v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/27/b9/27b9cfbb678630047f85e1adc55f7df7/0114455762.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/96/4d9621a180cfee96ba85d2da83163461/0105948132.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/05/3405327567eb345e9c0c326a590cd9ae/0105886699.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/89/22896600c7f19a5813fa824ee8207dd4/0122524970v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/cf/e7cf5a22f39eddc3235f047c566b747e/0122159010v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/c4/43c4067994de48347a260c6191e88528/0103046501v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/a1/74a1fcd5d60af69422390e97fbf77dcd/0109296819.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:quality(80)/p7i.vogel.de/wcms/c3/77/c3773763653a2c21d1bc56edaeb5ee28/0129073638v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)