Anbieter zum Thema

Verifikationsunterstützung in VHDL-2008

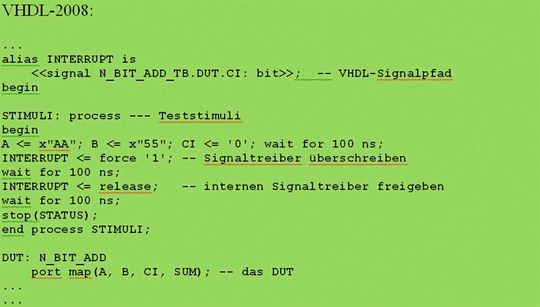

Der 2008-Standard erweitert die Möglichkeiten einer plattformunabhängigen Entwurfsverifikation durch Einführung neuer Schlüsselworte. So kann z.B. die Ausführung einer Testbench durch VHDL-Anweisungen unterbrochen (stop) bzw. beendet (finish) werden: Mit dem in Listing 5 vorgestellten VHDL-Code wird z.B. in ModelSim 10.4 die folgende Statusmeldung ausgegeben:

Break in Process STIMULI at … line …

Auch ist es möglich mit den neuen VHDL-Anweisungen force bzw. release den Wert von Signalen oder Variablen für Testzwecke zu überschreiben bzw. diese Simulations- treiber wieder freizugeben. Besonders vorteilhaft ist dies in Zusammenhang mit einer alias-Deklaration. So zeigt z.B. das Listing 5 die Testbench N_BIT_ADD_TB in der die Komponenteninstanz DUT verwendet wird. Das interne Signal CI dieser Komponente wird mit dem Alias-Namen INTERRUPT versehen wobei der vollständige Signalpfad in << … >> Klammern anzugeben ist. Innerhalb der Testbench wird der interne Signaltreiber durch den force-Befehl mit dem Wert 1 überschrieben und durch den release-Befehl nach 100 ns wieder freigegeben. Damit wird erreicht, dass die Komponente in diesem Zeitraum mit einem extern aufgezwungenen Signal simuliert.

Weitere Vereinfachungen gegenüber früheren Standards

Weitere Vereinfachungen, die VHDL-2008 gegenüber VHDL-2002 mit sich bringt, sind beispielsweise:

- Blockkommentare: Ähnlich wie in der Programmiersprache C ist es im nun erlaubt, Blockkommentare zu verwenden. Die bisherige Restriktion, dass Kommentare auf eine einzige Codezeile beschränkt sind, entfällt mit der Einführung der Kommentarbegrenzungssymbole /* und */.

- Bistring Konstanten: Bisher war eine Signalwertzuweisung von Hexadezimalzahlen mit dem Bezeichner X vor der Zahl nur dann möglich, wenn diese ein Vielfaches von 4 Bit umfassen. Im Standard VHDL-2008 entfällt diese Restriktion und es ist außerdem möglich, Zahlen vorzeichenlos, vorzeichenbehaftet oder dezimal zuzuweisen. Wenn die Zahlen die angegebene Bitbreite überschreiten, werden die höherwertigen Bits abgeschnitten. Wenn hingegen die Zahlen kleiner sind, als Bitstellen zur Verfügung stehen, werden je nach Datentyp führende Bitstellen mit Nullen bzw. vorzeichengerecht ergänzt.

- Signalausdrücke in port map Instanziierungen: Allgemein gilt, dass VHDL-2008 weniger global statische Ausdrücke benötigt als zuvor. Derartige Ausdrücke müssen erst beim Linken der einzelnen Komponenten des VHDL-Modells (Elaboration) einen festen Wert besitzen. So kann z.B. in einer port map Anweisung ein Boole’scher Ausdruck oder eine Datentypkonversion an die Komponenteninstanz übergeben werden.

- Bitweise Boole’sche Verknüpfungen: Die Boole’schen Operatoren and, or, xor, nand, nor und xnor können in VHDL-2008 auch unär, also mit einem einzelnen Signalvektor als Operand verwendet werden. Mit dieser Verwendung des Operators wird die bitweise Verknüpfung aller Bitelemente des Signalvektors gebildet.

- Verknüpfung skalarer Signale mit Signal-Arrays: Bisher war es erforderlich, dass die Bitbreiten aller Operanden eines Boole’schen Operators gleich sein mussten. Diese Restriktion gibt es in VHDL-2008 nicht mehr. So kann z.B. die UND-Verknüpfung aller Bits eines Signalvektors mit einem Freigabesignal EN in einer einzelnen Zuweisung realisiert werden. Signalarrays und skalare Signale dürfen also in Boole’schen Ausdrücken gemischt verwendet werden.

- Vereinfachte Bedingungsausdrücke: In vielen Bedingungsausdrücken war es erforderlich, einen expliziten Vergleich mit einer Signalwertkonstanten durchzuführen. Wie das Beispiel in Listing 3 zeigt ist dies in VHDL-2008 nicht mehr erforderlich.

- Bedingte Komponenteninstanziierung: Schon im bisherigen VHDL-Standard VHDL-2002 war es erlaubt, eine automatisierte Komponenteninstanziierung mit der generate-Anweisung nur bei Erfüllung einer bestimmten Bedingung durchzuführen. Neu ist im VHDL-2008 Standard nun, dass es auch erlaubt ist, der if-Abfrage einen else-Zweig hinzuzufügen. Ebenfalls ist es erlaubt, die automatisierte Komponenteninstanziierung abhängig von dem Wert einer case-Abfrage durchzuführen.

VHDL-2008 in Simulations- und Synthesewerkzeugen

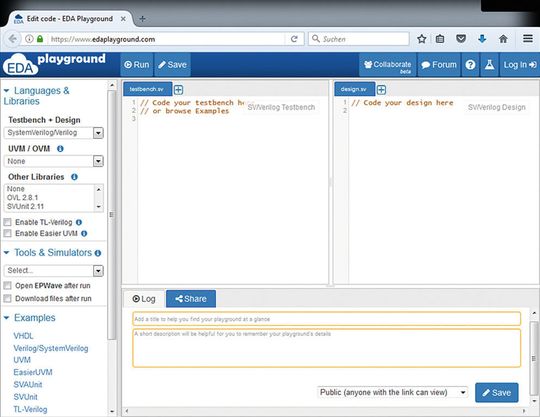

Eine einfache Möglichkeit, die Syntax der neuen Sprachkonstrukte auszuprobieren, ohne auf dem eigenen Rechner besondere Werkzeuge installieren zu müssen, bietet edaplayground.com von der Firma Doulos. Dort können verschiedene EDA Werkzeuge für Testzwecke evaluiert werden. U.a. kann auch der Aldec Simulator Riviera Pro mit der Option VHDL-2008 ausgewählt werden, der diesen Standard vollständig unterstützt.

Die ohne Anspruch auf Vollständigkeit erstellte Tabelle 1 zeigt, in welchem Umfang ein FPGA-Entwurf mit VHDL-2008 durch aktuelle Simulations- und Synthesewerkzeuge unterstützt wird. Da die meisten dieser Werkzeuge noch nicht für VHDL-2008 vorkonfiguriert sind, müssen an geeigneter Stelle Einstellungen vorgenommen werden, um diesen Standard auszuwählen. Weitergehende Information über die notwendigen Konfigurationen, bzw. darüber, welche der neuen Sprachkonstrukte ggf. noch nicht unterstützt werden, müssen der jeweiligen Dokumentation entnommen werden.

Zusammenfassend kann festgehalten werden, dass VHDL-2008 im Vergleich zu älteren VHDL-Standards folgende Vorteile bietet:

- Eine Reduzierung des Codierungsaufwands und damit eine leichtere Lesbarkeit des VHDL-Codes durch die Einführung neuer Operatoren und die Aufgabe bisher gültiger Restriktionen.

- Die garantierte Konsistenz der Simulations- und Synthesesemantik für kombinatorische Logik.

- Neue, synthesefähige Datentypen für eine einfache Festkommaarithmetik, die insbesondere die Umsetzung von Algorithmen der digitalen Signalverarbeitung vereinfacht.

- Eine größere Flexibilität bei einer plattformunabhängigen Verifikation durch VHDL-Testbenches.

Die Tatsache, dass die aktuellen EDA-Werkzeuge VHDL-2008 umfassend unterstützen, sollte also künftig keine Ausrede mehr dafür sein, auf die Vorteile dieses neuen Standards zu verzichten.

[1] Jürgen Reichardt: Digitaltechnik, Eine Einführung mit VHDL, 4. Auflage. De Gruyter, Oldenbourg Verlag, 2016

[2] Jim Lewis: VHDL-2008 The End of Verbosity,

URL: http://www.synthworks.com/papers/VHDL_2008_end_of_verbosity_2013

[3] IEEE: 1076-2008 – IEEE Standard VHDL Language Reference Manual,

URL: http://standards.ieee.org/findstds/standard/1076-2008.html

* * Prof. Dr. Jürgen Reichardt st Dozent für IT, Schwerpunkte Digitaler Systementwurf, HW-SW-Codesign und FPGA-basierter SoC-Entwurf, an der HAW Hamburg.

(ID:45610702)

:quality(80)/p7i.vogel.de/wcms/b8/20/b8203d9f2b6f6e61bff6c3fda15042d3/0128235802v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/90/79901d8c1934b11223a53cb900b1aa85/das-20building-2092-20bei-20der-20microsoft-zentrale-20in-20redmond-20--20quelle-20coolcaesar-20via-20wikimedia-20commons-5184x2915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/92/3192d2bddbdb052afd8904128dd7aec1/0123884994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/42/b04293b683f177fa6c781c1e00e1770f/0122968330v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/ea/acea3ca6c15e0bd261c8bde5d3fe7bfb/0127825678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/d9/93d9211463a0af86eff0b83c359cd880/0127528428v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/c1/d9c121f0680f16e547502038f5c26481/0130027942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/3d/753d0fa44b344d363e25c91dc0752635/0129134302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9a/ef9a10566eaa807a8fdad9cbff80246f/0126533084v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/f5/47f5a305c48bfcaf3daae7e6b7478a0f/0131065910v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/a8/a9a87353e49fb7432ce35aef31d06ad6/0130134372v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/b2/1eb228a11ff793648167b84e30da4eb3/0129529708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/0a/df0a16a8a74519cf7e4ae26b468a8326/0129511289v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/23/2323167fce16d7a31011ac17a97933c9/0129855253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/e0/5fe00181ea62f890f53af36d03782612/0129630465v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/92/6f92cb791d67b866650a432e847ad8f2/0129693241v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/0e/f30ed4c0e762a250c39013170f3d154a/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/b2/2eb2a82d215c72f59c1fde532c092e87/0131010297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/a7/44a7069736629cbbfa41b74af865ec67/0130322397v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/8c/718c0df3cae4339bb3ea0b799b53e1cd/0131015301v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/21/b12113e8d5357060593e78ad3e396773/0130960706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/f0/4cf066b46a5fcfc430a2454a5e82e801/0129279386v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/27/b9/27b9cfbb678630047f85e1adc55f7df7/0114455762.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/96/4d9621a180cfee96ba85d2da83163461/0105948132.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/05/3405327567eb345e9c0c326a590cd9ae/0105886699.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/89/22896600c7f19a5813fa824ee8207dd4/0122524970v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/cf/e7cf5a22f39eddc3235f047c566b747e/0122159010v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/c4/43c4067994de48347a260c6191e88528/0103046501v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/a1/74a1fcd5d60af69422390e97fbf77dcd/0109296819.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:quality(80)/p7i.vogel.de/wcms/c3/77/c3773763653a2c21d1bc56edaeb5ee28/0129073638v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)