Anbieter zum Thema

CPU-Frequenz und Spannungsregelung

Der Stromverbrauch eines CMOS-Logikbausteins wird theoretisch durch folgende Formel ausgedrückt: P = f x U^2 x k, wobei f die Taktfrequenz ist, U die Spannung in Volt; k ist eine Konstante.

Beim Power Debugging kann der Entwickler den Stromverbrauch anhand der Taktfrequenz analysieren. Ein System, das bei einer Taktfrequenz von 50 MHz nahezu keine Zeit im Stromsparmodus verbringt, sollte bei 100 MHz etwa 50 Prozent der Laufzeit im Stromsparmodus bleiben. Die Leistungsdaten im Debugger ermöglichen es dem Entwickler, dieses erwünschte Verhalten zu überprüfen. Bei nichtlinearer Abhängigkeit von der Taktfrequenz lässt sich so die ideale Taktfrequenz bestimmen, bei der die Energieaufnahme am geringsten ist.

Seit kurzer Zeit ist es bei manchen CPUs möglich, die interne Spannungsversorgung des Rechenkerns aus einer Anwendung heraus zu beeinflussen. So lässt sich bei einem System die VCORE beispielsweise von 1,8 auf 1,2 Volt senken und gleichzeitig die Taktfrequenz auf bis zu 4 MHz hochsetzen. Diese Technik ist vergleichbar mit den in Desktop- und Mobilprozessoren verwendeten Technologien, beispielsweise Intels Speedstep.

Die Möglichkeit, die Spannungs-Komponente der obigen Gleichung zu beeinflussen, eröffnet völlig neue Möglichkeiten, ein System für geringen Energieverbrauch zu optimieren. Das Potenzial ist riesig: Das Senken der Taktfrequenz von 32 auf 4 MHZ senkt den Stromverbrauch um Faktor 8. Wird gleichzeitig VCORE von 1,8 auf 1,2 Volt gesenkt, ergibt sich eine Ersparnis um das 18-fache.

Ein Beispiel mit Interrupts zeigt eine weitere Situation, in der ein überhöhter Stromverbrauch schwierig nachzuvollziehen ist.

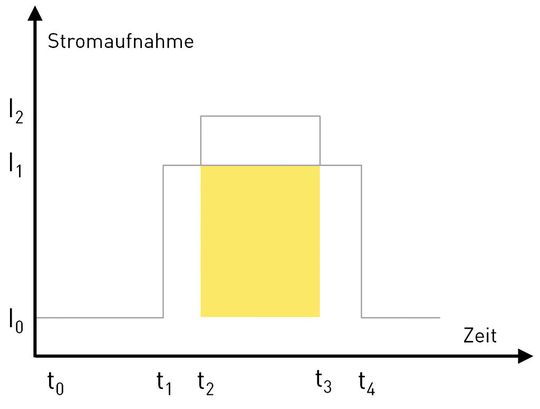

Das folgende Bild zeigt ein schematisches Diagramm der Stromaufnahme eines ereignisgesteuerten Systems, wobei das System bei t0 in einem inaktiven Zustand ist, der Strom liegt bei I0. Bei t1 wird das System aktiviert, der Strom steigt auf I1, das ist die Stromaufnahme des aktiven Systems mit einer genutzten Peripherieeinheit. Bei t2 wird die Ausführung durch einen Interrupt mit höherer Priorität unterbrochen. Peripheriegeräte, die der neue Thread nicht benötigt, werden nicht abgeschaltet, stattdessen werden durch den neuen Thread zusätzliche Einheiten aktiviert. Damit steigt der Strom in der Zeit zwischen t2 und t3 auf I2. Bei t3 wird die Kontrolle an den niedriger priorisierten Thread zurückgegeben.

Die Funktionalität des Beispielsystems kann exzellent sein, Codegröße und Ausführungsgeschwindigkeit optimal. Nichtsdestotrotz lässt sich der Energieverbrauch weiter optimieren. Die gelbe Fläche repräsentiert die Energie, die sich durch das Abschalten der ungenutzten Peripherie oder das Ändern der Prioritäten zwischen t2 und t3 hätte sparen lassen.

Durch Power Debugging wäre es einfach gewesen, den außergewöhnlichen Anstieg des Stromverbrauchs beim Schalten des Interrupts zu bemerken und als unnormal zu erkennen. Eine genauere Untersuchung im Timeline-Fenster hätte gezeigt, dass ungenutzte Peripherieeinheiten aktiv sind und länger als nötig Energie verbrauchen. Es wäre eine Untersuchung gefolgt, ob es sinnvoll gewesen wäre, in Situationen wie der beschriebenen zusätzliche Taktzyklen für das Ab- und Anschalten der Peripherie zu verwenden

Falsche Hardwarekonfiguration

Um potentialfreie Eingänge zu vermeiden, ist es übliche Praxis in der Hardwareentwicklung, ungenutzte I/O-Pins des Mikrocontrollers auf Erde zu legen. Konfiguriert nun die Software einen dieser geerdeten Pins irrtümlich als Ausgang mit einer logischen „1“, kann ein Strom von bis zu 25 mA an diesem Pin abfließen. Dieser hohe, unerwartete Abfluss wird im Stromdiagramm schnell erkannt. Auch die zugehörige falsche Initialisierung lässt sich beim Beobachten des Anwendungsstarts im Stromdiagramm einfach identifizieren. Eine ähnliche Situation entsteht, wenn ein I/O-Pin als Eingang definiert und von einem externen Schaltkreis gespeist, von der Software aber irrtümlich als Ausgang konfiguriert wird.

Analoge Interferenzen

Das Mischen analoger und digitaler Stromkreise auf einer Platine birgt viele Herausforderungen. Das Board-Design und -Routing werden wichtig, um analoge Rauschpegel niedrig zu halten und ein exaktes Auswerten der Analogsignale zu ermöglichen. Ein gutes gemischtes Design erfordert eine sorgfältige Auswahl der Hardware und viel Erfahrung. Auch die Software kann die Qualität der analogen Messungen beeinflussen. Eine hohe I/O-Aktivität in Zeitspannen, in denen analoge Signale ausgelesen werden, führt dazu, dass in dieser Zeit viele digitale Leitungen ihren Zustand ändern. Dies kann zusätzliches Rauschen am A/D-Wandler verursachen.

Mit Hilfe von Power Debugging lassen sich Interferenzen aus digitalen und Stromversorgungsleitungen in die analogen Bereiche erkennen. Wird die Interrupt-Aktivität im Timeline-Fenster gemeinsam mit Energiedaten dargestellt, lässt sich im Stromdiagramm der zeitliche Bereich direkt vor den A/D-Wandler-Interrupts untersuchen. Spannungsspitzen in der Nähe von A/D-Wandleraktivität können Rauschen verursachen und müssen untersucht werden. Da die Daten in der Timeline mit dem ausgeführten Code verknüpft sind, führt ein Doppelklick auf eine verdächtige Strommessung direkt zum entsprechenden C-Quellcode.

Die beschriebene Power Debugging-Technologie ermöglicht es dem Entwickler, den Ablauf und Code einer Anwendung in Bezug auf den Energieverbrauch zu analysieren. Mit den Erkenntnissen daraus lässt sich der Quellcode so synchronisieren und optimieren, dass die Energieanforderungen so gering wie möglich sind. Auf diese Weise stellen Software-Entwickler sicher, dass ihr Projekt so stromsparend wie möglich ist, ohne die Leistungsfähigkeit der Anwendung einzuschränken.

Die Power Debugging-Technologie von IAR Systems ermöglicht es dem Entwickler, den Ablauf und Code einer Anwendung in Bezug auf den Energieverbrauch zu analysieren. Mit den Erkenntnissen lässt sich der Quellcode so synchronisieren und optimieren, dass die Energieanforderungen so gering wie möglich sind. Auf diese Weise stellen Software-Entwickler sicher, dass ihr Projekt so viel Strom wie möglich spart, ohne die Leistungsfähigkeit der Anwendung einzuschränken. //FG

* * Lotta Frimansson ist Produktmanagerin bei IAR Systems. Sie lebt und arbeitet in Uppsala/Schweden.

* * Anders Lundgren ist Produktmanager bei IAR Systems. Er lebt und arbeitet in Uppsala/Schweden.

(ID:39444320)

:quality(80)/p7i.vogel.de/wcms/b8/20/b8203d9f2b6f6e61bff6c3fda15042d3/0128235802v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/90/79901d8c1934b11223a53cb900b1aa85/das-20building-2092-20bei-20der-20microsoft-zentrale-20in-20redmond-20--20quelle-20coolcaesar-20via-20wikimedia-20commons-5184x2915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/92/3192d2bddbdb052afd8904128dd7aec1/0123884994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/42/b04293b683f177fa6c781c1e00e1770f/0122968330v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/ea/acea3ca6c15e0bd261c8bde5d3fe7bfb/0127825678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/d9/93d9211463a0af86eff0b83c359cd880/0127528428v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/c1/d9c121f0680f16e547502038f5c26481/0130027942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/3d/753d0fa44b344d363e25c91dc0752635/0129134302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9a/ef9a10566eaa807a8fdad9cbff80246f/0126533084v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/a8/a9a87353e49fb7432ce35aef31d06ad6/0130134372v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/b2/1eb228a11ff793648167b84e30da4eb3/0129529708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/0a/df0a16a8a74519cf7e4ae26b468a8326/0129511289v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/f0/4cf066b46a5fcfc430a2454a5e82e801/0129279386v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/23/2323167fce16d7a31011ac17a97933c9/0129855253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/e0/5fe00181ea62f890f53af36d03782612/0129630465v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/92/6f92cb791d67b866650a432e847ad8f2/0129693241v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c3/77/c3773763653a2c21d1bc56edaeb5ee28/0129073638v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/0e/f30ed4c0e762a250c39013170f3d154a/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/b2/2eb2a82d215c72f59c1fde532c092e87/0131010297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/a7/44a7069736629cbbfa41b74af865ec67/0130322397v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/8c/718c0df3cae4339bb3ea0b799b53e1cd/0131015301v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/21/b12113e8d5357060593e78ad3e396773/0130960706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/27/b9/27b9cfbb678630047f85e1adc55f7df7/0114455762.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/96/4d9621a180cfee96ba85d2da83163461/0105948132.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/05/3405327567eb345e9c0c326a590cd9ae/0105886699.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/89/22896600c7f19a5813fa824ee8207dd4/0122524970v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/cf/e7cf5a22f39eddc3235f047c566b747e/0122159010v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/c4/43c4067994de48347a260c6191e88528/0103046501v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/a1/74a1fcd5d60af69422390e97fbf77dcd/0109296819.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:fill(fff,0)/p7i.vogel.de/companies/66/1c/661cd4860acd6/emlix-logo-300x210mm-150dpi-rgb.png)

:fill(fff,0)/p7i.vogel.de/companies/63/8f/638f6ed06f4c8/parasoft-logo-2018.png)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)