Multicore-Mikrocontroller-Wahl, Teil 3 Sind die vorhandenen Ressourcen in der Peripherie ausreichend?

Nach der Untersuchung der Anforderungen des Projektes hinsichtlich funktionaler Sicherheit (Safety) und Datensicherheit (Security) befasst sich der letzte Schritt mit den Peripherie-Bausteinen: Was brauche ich an Pins, Speicher oder Bussystemen?

Anbieter zum Thema

Die ausreichende Pin-Anzahl ist neben der zur Verfügung stehenden Rechenkapazität ein entscheidender Faktor für den Erfolg eines Projektes. Alle Mikrocontroller haben eine Einschränkung gemeinsam: Es gibt in der Regel immer mehr Peripherie-Funktionen als verfügbare Pins.

Einige Mikrocontroller werden bei gleichem internem Silizium mit unterschiedlichen Gehäuse-Typen angeboten. Gehäuse mit weniger Pins sind typischerweise kostengünstiger und benötigen obendrein weniger Platz auf der Baugruppe. Weniger Pins bedeuten aber gleichzeitig, dass weniger Peripherie-Funktionen von außen sichtbar oder von außen ansprechbar sind bzw. nach außen wirken können. Eine Kernaufgabe ist hier also die Untersuchung, ob die zwingend benötigten Peripherie-Module auch alle über die erforderlichen Ports-Pins verfügen.

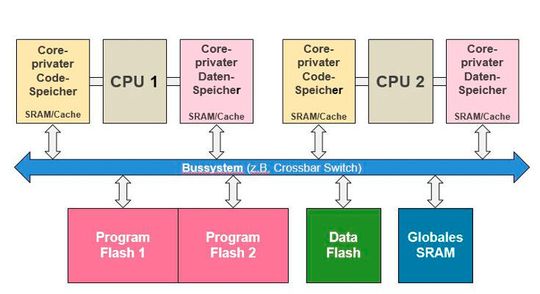

Performance-Steigerung durch Core-private Speicher

Die Multicore-Mikrocontroller-Architekturen unterscheiden sich maßgeblich voneinander in der Speicher-Implementierung. Die Optionen sind in der Regel:

- viel globaler Speicher und wenig Core-lokaler Speicher, oder

- wenig globaler Speicher und viel Core-lokaler Speicher

Wird sehr hohe Rechenperformance benötigt, kann dies durch viele Core-lokale Speicher und eine hohe Core-Taktung erreicht werden. Ferner können die Programme in lokalen Speichern besser vor unberechtigtem Zugriff anderer Cores gesichert werden.

Das On-chip-Bussystem – eine Performance-Bremse?

Bussysteme, die nur serielle Kommunikation erlauben, können sich schnell zu einem „Bottleneck“ in der Applikation entwickeln, wenn viele Daten kommuniziert werden müssen. So kann es z.B. bei der Anwendung von Ethernet-Modulen vorkommen, dass diese Einheiten in der Regel nicht über genug privaten Speicher verfügen.

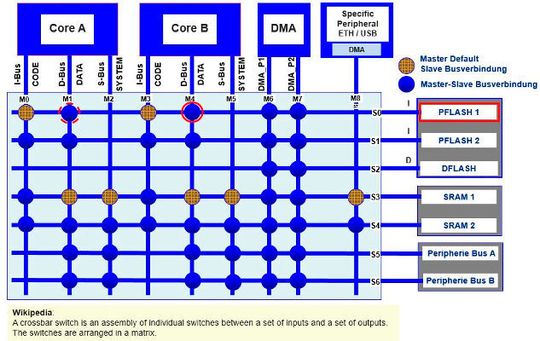

Besser sind die Implementierungen von Bus-Matrix-Systemen, wie z.B. einem Crossbar-Switch. Diese Implementierung wird heute als Bus-Interface für die Verbindung von Cores zu den globalen Ressourcen eingesetzt. Meist sind alle Peripherie-Module über ein gemeinsames oder zwei serielle Bussysteme angeschlossen.

Zur Verhinderung von unliebsamen Überraschungen lohnt sich eine Performance-Analyse an den verwendeten Bussystemen, damit es in der realen Anwendung nicht zu unerwarteten Kommunikationsverzögerungen kommen kann.

Fazit

Für einen erfolgreichen Umstieg einer Hard-Realtime-Applikation mit Singlecore nach Multicore ist ein Ressourcen-Management bei der Mikrocontroller-Auswahl sehr ratsam.

:quality(80)/images.vogel.de/vogelonline/bdb/1191800/1191837/original.jpg)

Multicore-Mikrocontroller-Wahl, Teil 1

Anhand der Projekt-Ressourcen den richtigen Multicore-MCU wählen

:quality(80)/images.vogel.de/vogelonline/bdb/1187400/1187425/original.jpg)

Multicore-Mikrocontroller-Wahl, Teil 2

Welche Safety- und Securityanforderungen zählen bei der MCU-Wahl?

* Dipl.-Ing. Ingo Pohle ist Mitgründer und Geschäftsführer der MicroConsult GmbH.

* Dipl.-Ing. Marcus Gößler ist Trainer und Coach im Bereich Embedded, mit Schwerpunkten auf sicherheitsrelevanten Anwendungen und Multicore-Bausteinen Systems, bei Microconsult.

(ID:44548440)

:quality(80)/p7i.vogel.de/wcms/b8/20/b8203d9f2b6f6e61bff6c3fda15042d3/0128235802v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/90/79901d8c1934b11223a53cb900b1aa85/das-20building-2092-20bei-20der-20microsoft-zentrale-20in-20redmond-20--20quelle-20coolcaesar-20via-20wikimedia-20commons-5184x2915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/92/3192d2bddbdb052afd8904128dd7aec1/0123884994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/42/b04293b683f177fa6c781c1e00e1770f/0122968330v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/ea/acea3ca6c15e0bd261c8bde5d3fe7bfb/0127825678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/d9/93d9211463a0af86eff0b83c359cd880/0127528428v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/c1/d9c121f0680f16e547502038f5c26481/0130027942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/3d/753d0fa44b344d363e25c91dc0752635/0129134302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9a/ef9a10566eaa807a8fdad9cbff80246f/0126533084v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/47/f5/47f5a305c48bfcaf3daae7e6b7478a0f/0131065910v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/a8/a9a87353e49fb7432ce35aef31d06ad6/0130134372v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/b2/1eb228a11ff793648167b84e30da4eb3/0129529708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/0a/df0a16a8a74519cf7e4ae26b468a8326/0129511289v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/23/2323167fce16d7a31011ac17a97933c9/0129855253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/e0/5fe00181ea62f890f53af36d03782612/0129630465v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/92/6f92cb791d67b866650a432e847ad8f2/0129693241v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/0e/f30ed4c0e762a250c39013170f3d154a/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/b2/2eb2a82d215c72f59c1fde532c092e87/0131010297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/a7/44a7069736629cbbfa41b74af865ec67/0130322397v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/8c/718c0df3cae4339bb3ea0b799b53e1cd/0131015301v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/21/b12113e8d5357060593e78ad3e396773/0130960706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/f0/4cf066b46a5fcfc430a2454a5e82e801/0129279386v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/27/b9/27b9cfbb678630047f85e1adc55f7df7/0114455762.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/96/4d9621a180cfee96ba85d2da83163461/0105948132.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/05/3405327567eb345e9c0c326a590cd9ae/0105886699.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/89/22896600c7f19a5813fa824ee8207dd4/0122524970v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/cf/e7cf5a22f39eddc3235f047c566b747e/0122159010v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/c4/43c4067994de48347a260c6191e88528/0103046501v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/a1/74a1fcd5d60af69422390e97fbf77dcd/0109296819.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4f/d9/4fd906332667dcaa522746945c446ab6/0128755214v1.jpeg)