Anbieter zum Thema

Tief eingebettetes Debugging

Vor allem Applikationen, die ihre einzelnen Aufgaben mit hohen Echtzeitanforderungen und verteilt auf unterschiedliche Rechenkerne abarbeiten, stellen für Debugging, Test und Systemanalyse oftmals eine große Herausforderung dar. So wirken sich die im Normalfall zumeist ziemlich großen Abhängigkeiten zwischen den auf unterschiedlichen Kernen ausgeführten Tasks natürlich auf das Stop-Go-Debugging aus. Man kann nicht einfach unbedacht einen Kern anhalten, während alle anderen weiterlaufen.

Mitunter müssen auch die restlichen Kerne und die Peripherals gleichzeitig angehalten werden, damit die Applikation nicht gänzlich außer Trittin einen undefinierten Zustand gerät. Dumm nur, dass bei heterogenen Kernen mit unterschiedlicher Taktung und Ausführungs-Pipelines ein gleichzeitiges Anhalten gar nicht so einfach ist. Deshalb wird es in der Praxis immer einen gewissen Zeitversatz geben, mit dem man als Entwickler leben muss. Manchmal kann das Anhalten eines kompletten Multicore-Systems sogar fatale Folgen haben, zum Beispiel, wenn parallel noch andere Anwendungen laufen, die zu diesen Zeitpunkt nicht debuggt werden sollen oder dürfen. Die genannten Anwendungsszenarien lassen erahnen, wie wichtig ein flexibles, synchrones Run-Control für die Multicore-Debug-Infrastruktur ist.

Ein zweiter, bedeutsamer Aspekt ist die Analyse des Laufzeitverhaltens, und zwar ohne dabei selbiges zu beeinflussen. Diese nicht-intrusive Systembeobachtung spielt nicht nur bei echtzeitkritischen Anwendungen, sondern auch bei Profiling-Aufgaben oder der Kommunikationsbeobachtung zwischen den Kernen eine wichtige Rolle. Oftmals ist es wünschenswert, den jeweiligen Systemzustand zu einem bestimmten Zeitpunkt mit Hilfe des extern angeschlossenen Debuggers aus dem Target-System auslesen zu können. Ein Anhalten der Applikation würde das Systemverhalten unter Umständen allerdings so grundlegend verändern, dass es nichts mehr mit dem Zustand ohne angeschlossenen Debugger zu tun hätte. Daraus folgt: Für eine effiziente nicht-intrusive Systembeobachtung ist Tracen unerlässlich.

On-Chip Debugger

Doch zuerst noch einmal zurück zum Thema synchrones Run-Control. Hierfür sind schnelle Signalwege zwischen den Kernen not¬wendig, die sich nur mit Debug-Hardware direkt auf dem Chip realisieren lassen. Stop- und Go-Signale von extern über die Debug-Schnittstelle zu übermitteln, würde bei den heutzutage üblichen hohen Taktfrequenzen viel zu lange dauern. Die Applikation käme unweigerlich außer Tritt.

Nun bietet jeder Chip-Hersteller erfahrungsgemäß seine eigene On-Chip Debug-Lösung an. Infineon beispielsweise nennt sie OCDS. Ein wichtiger Bestandteil dieses OCDS ist der implementierte Trigger-Switch, der Halt- und Suspend-Signale einzeln konfigurierbar systemweit verteilt. Der Trigger-Switch erlaubt es, einzelne Rechenkerne und Periphiereieeinheiten ohne Beeinfussung der restlichen Funktionsgruppen ganz gezielt gleichzeitig anzuhalten bzw. wieder zu starten. Zusätzlich können einzelne Trigger-Leitungen des Trigger-Switches auch über Pins nach außen geführt werden. Die ermöglicht interessante Optionen wie beispielsweise den Anschluss eines Oszilloskops oder die externe Auslösung eines Breaks.

Neben der AURIX-Familie von Infineon gibt es natürlich noch eine Vielzahl anderer Multicore-Mikrocontroller, die den Industrial- und Automotive Sektor abdecken, darunter beispielsweise SoCs auf Basis der ARM-Cortex-R-Architektur oder Freescales MPC57xx-Familie. Werfen wir als erstes einen Blick auf den CoreSight-Baukasten [1] von ARM.

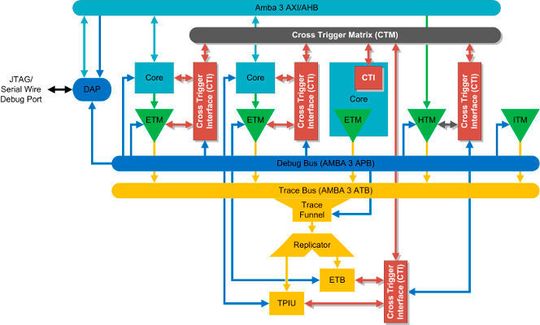

Für die Verteilung der Break- und Go-Signale zwischen den Kernen wird eine sogenannte Cross-Trigger-Matrix (CTM) mit daran angeschlossenen Cross-Trigger-Interfaces (CTI) genutzt (siehe Bild). Kanäle in der CTM leiten die Signale im Broadcast-Modus an die angeschlossenen CTIs weiter. Diese sind wiederum direkt mit den Kernen verbunden und so konfigurierbar, dass sie die Signale für das Run-Control zwischen Kern und CTM wahlweise entweder weiterleiten oder blockieren. Aufgrund der notwendigen Handshake-Mechanismen zwischen den beteiligten Komponenten kommt es dabei üblicherweise zu Signalverzögerungen von mehreren Takten. Wie groß diese Verzögerungen tatsächlich sind, hängt von der jeweiligen Implementierung und natürlich der Taktung der einzelnen Komponenten ab.

Komplett vermeiden lässt sich der beim synchronen Anhalten entstehende Schlupf von einigen wenigen, typischerweise im einstelligen Bereich angesiedelten Befehlen jedoch auch durch die CTM nicht. Außerdem ist es dem jeweiligen Chip-Hersteller seitens ARM freigestellt, ob er die notwendigen CoreSight-Komponenten überhaupt auf dem Chip implementiert.

Auch von den Power-Architecture-basierten Controllern der MPC57xx-Familie wird das synchrone Run-Control bereits hardwareseitig unterstützt. Die dafür verantwortliche Einheit heißt DCI (Debug and Calibration Interface). Der Vorteil gegenüber der ARM-Lösung: Wie beim Trigger-Switch des AURIX sind auch beim DFI die Peripherieeinheiten gleich mit angeschlossen, was ein Anhalten des gesamten Systems und nicht nur der Kerne erlaubt.

(ID:43763028)

:quality(80)/p7i.vogel.de/wcms/b8/20/b8203d9f2b6f6e61bff6c3fda15042d3/0128235802v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/79/90/79901d8c1934b11223a53cb900b1aa85/das-20building-2092-20bei-20der-20microsoft-zentrale-20in-20redmond-20--20quelle-20coolcaesar-20via-20wikimedia-20commons-5184x2915v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/31/92/3192d2bddbdb052afd8904128dd7aec1/0123884994v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b0/42/b04293b683f177fa6c781c1e00e1770f/0122968330v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cc/53/cc53ebfd9f45b28eb918a8098b63846b/0127825678v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/ea/acea3ca6c15e0bd261c8bde5d3fe7bfb/0127825678v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/93/d9/93d9211463a0af86eff0b83c359cd880/0127528428v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d9/c1/d9c121f0680f16e547502038f5c26481/0130027942v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/75/3d/753d0fa44b344d363e25c91dc0752635/0129134302v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ef/9a/ef9a10566eaa807a8fdad9cbff80246f/0126533084v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/a9/a8/a9a87353e49fb7432ce35aef31d06ad6/0130134372v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/1e/b2/1eb228a11ff793648167b84e30da4eb3/0129529708v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/df/0a/df0a16a8a74519cf7e4ae26b468a8326/0129511289v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/4c/f0/4cf066b46a5fcfc430a2454a5e82e801/0129279386v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/23/23/2323167fce16d7a31011ac17a97933c9/0129855253v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5f/e0/5fe00181ea62f890f53af36d03782612/0129630465v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/92/6f92cb791d67b866650a432e847ad8f2/0129693241v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c3/77/c3773763653a2c21d1bc56edaeb5ee28/0129073638v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/f3/0e/f30ed4c0e762a250c39013170f3d154a/0131041847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2e/b2/2eb2a82d215c72f59c1fde532c092e87/0131010297v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/44/a7/44a7069736629cbbfa41b74af865ec67/0130322397v4.jpeg)

:quality(80)/p7i.vogel.de/wcms/eb/23/eb23785d23e0a13df6f6344f6d880bd0/0129487941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/71/8c/718c0df3cae4339bb3ea0b799b53e1cd/0131015301v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b1/21/b12113e8d5357060593e78ad3e396773/0130960706v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/0d/e8/0de88d8542d1b2b5deddf20789bccc2c/0130537290v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9f/9d/9f9d8357928662c1173bad86e63f0fb0/0126749087v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/27/b9/27b9cfbb678630047f85e1adc55f7df7/0114455762.jpeg)

:quality(80)/p7i.vogel.de/wcms/4d/96/4d9621a180cfee96ba85d2da83163461/0105948132.jpeg)

:quality(80)/p7i.vogel.de/wcms/34/05/3405327567eb345e9c0c326a590cd9ae/0105886699.jpeg)

:quality(80)/p7i.vogel.de/wcms/22/89/22896600c7f19a5813fa824ee8207dd4/0122524970v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/e7/cf/e7cf5a22f39eddc3235f047c566b747e/0122159010v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/43/c4/43c4067994de48347a260c6191e88528/0103046501v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/74/a1/74a1fcd5d60af69422390e97fbf77dcd/0109296819.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/66/f6/66f673630a98a/logo-mc-rgb-300x300.png)

:quality(80)/p7i.vogel.de/wcms/93/b2/93b2dee2b42d98849c80562a53d8b31e/0128754755v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/d7/bad734452b1b8360591396b49da37b72/0130644400v1.jpeg)